# **Tutorial on Remaining part of 8085 Microprocessor**

Dear students this tutorial is in continuation of lectures we have already discussed in the classroom.

## The 8085 Programming Model:

As we have already discussed in the class, the 8085 programming model includes six registers, one accumulator, and one flag register, as shown in Figure given below. In addition, it has two 16-bit registers: the stack pointer and the program counter. They are described below in brief.

| ACCUMULATOR A           | (8)          |          | FLAG      | REGISTER   |            |

|-------------------------|--------------|----------|-----------|------------|------------|

| В                       | (8)          |          | С         |            | (8)        |

| D                       | (8)          |          | E         |            | (8)        |

| Н                       | (8)          |          | L         |            | (8)        |

| :                       | Stack Pointe | er (SP)  |           |            | (16)       |

| Pro                     | ogram Coun   | ter (PC) |           |            | (16)       |

| Data Bus<br>8 Lines Bio | directional  | 1        | 6 Lines u | nidirectio | Address Bu |

## Registers

The 8085 has six general - purpose registers to store 8-bit data; these are identified as B, C, D, E, H and L as shown in the figure. They can be combined as register pairs - BC, DE, and HL - to perform some 16-bit operations. The programmer can use these registers to store or copy data into the registers by using data copy instructions.

## Accumulator

The accumulator is an 8-bit register that is a part of arithmetic/logic unit (ALU). This register is used to store 8-bit data and to perform arithmetic and logical operations. The result of an operation is stored in the accumulator. The accumulator is also identified as register A.

## Flags

The ALU includes five flip-flops, which are set or reset after an operation according to data conditions of the result in the accumulator and other registers. They are called Zero (Z), Carry (CY), Sign (S), Parity (P), and Auxiliary Carry (AC) flags; their bit positions in the flag register are shown in the Figure below. The most commonly used flags are Zero, Carry, and Sign. The microprocessor uses these flags to test data conditions.

|    | <u> </u> |    |    |    |    |    |    |

|----|----------|----|----|----|----|----|----|

|    |          |    |    |    |    |    |    |

| D7 | D6       | D5 | D4 | D3 | D2 | D1 | D0 |

| S  | Z        |    | AC |    | Р  |    | CY |

For example, after an addition of two numbers, if the sum in the accumulator id larger than

eight bits, the flip-flop uses to indicate a carry - called the Carry flag (CY) is set to one. When an arithmetic operation results in zero, the flip-flop called the Zero (Z) flag is set to one. The first Figure shows an 8-bit register, called the flag register, adjacent to the accumulator. However, it is not used as a register; five bit positions out of eight are used to store the outputs of the five flip-flops. The flags are stored in the 8-bit register so that the programmer can examine these flags (data conditions) by accessing the register through an instruction.

These flags have critical importance in the decision-making process of the micro- processor. The conditions (set or reset) of the flags are tested through the software instructions. For example, the instruction JC (Jump on Carry) is implemented to change the sequence of a program when CY flag is set. The thorough understanding of flag is essential in writing assembly language programs.

#### **Program Counter (PC)**

This 16-bit register deals with sequencing the execution of instructions. This register is a memory pointer. Memory locations have 16-bit addresses, and that is why this is a 16-bit register. The microprocessor uses this register to sequence the execution of the instructions. The function of the program counter is to point to the memory address from which the next byte is to be fetched. When a byte (machine code) is being fetched, the program counter is incremented by one to point to the next memory location

#### Stack Pointer (SP)

The stack pointer is also a 16-bit register used as a memory pointer. It points to a memory location in R/W memory, called the stack. The beginning of the stack is defined by loading 16-bit address in the stack pointer.

#### The 8085 Addressing Modes

The instructions MOV B, A or MVI A, 82H are to copy data from a source into a destination. In these instructions the source can be a register, an input port, or an 8-bit number (00H to FFH). Similarly, a destination can be a register or an output port. The sources and destination are operands. The various formats for specifying operands are called the ADDRESSING MODES. For 8085, they are:

- 1. Immediate addressing.

- 2. Register addressing.

- 3. Direct addressing.

- 4. Indirect addressing.

#### **Immediate addressing**

Data is present in the instruction. Load the immediate data to the destination provided. Example: MVI R, data

## **Register addressing**

Data is provided through the registers. Example: MOV Rd, Rs

#### **Direct addressing**

Used to accept data from outside devices to store in the accumulator or send the data stored in the accumulator to the outside device. Accept the data from the port 00H and store them into the accumulator or Send the data from the accumulator to the port 01H. Example: IN 00H or OUT 01H

# Indirect Addressing

This means that the Effective Address is calculated by the processor. And the contents of the address (and the one following) is used to form a second address. The second address is where the data is stored. Note that this requires several memory accesses; two accesses to retrieve the 16-bit address and a further access (or accesses) to retrieve the data which is to be loaded into the register.

# For instruction Set this is in continuation of the part which we have already discussed in the class.

# **Instructions Set:**

An **instruction** is a binary pattern designed inside a microprocessor to perform a specific function. The entire group of instructions, called the **instruction set**, determines what functions the microprocessor can perform. These instructions can be classified into the following five functional categories: data transfer (some time also called as copy) operations, arithmetic operations, logical operations, branching operations, and machine-control operations.

# **DATA TRANSFER INSTRUCTIONS**

| Opcode           | Operand                                             | Description                                                                                                                                                                                                                                                                                              |

|------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Copy from<br>MOV | n source to destination<br>Rd, Rs<br>M, Rs<br>Rd, M | This instruction copies the contents of the source<br>register into the destination register; the contents of<br>the source register are not altered. If one of the operands is a<br>memory location, its location is specified by the contents of<br>the HL registers.<br>Example: MOV B, C or MOV B, M |

| Move imr         | nediate 8-bit                                       |                                                                                                                                                                                                                                                                                                          |

| MVI              | Rd, data<br>M, data                                 | The 8-bit data is stored in the destination register or<br>memory. If the operand is a memory location, its location is<br>specified by the contents of the HL registers.<br>Example: MVI B, 57H or MVI M, 57H                                                                                           |

| Load accu        | imulator                                            |                                                                                                                                                                                                                                                                                                          |

| LDA              | 16-bit address                                      | The contents of a memory location, specified by a<br>16-bit address in the operand, are copied to the accumulator.<br>The contents of the source are not altered.<br>Example: LDA 2034H                                                                                                                  |

| Load accu        | mulator indirect                                    |                                                                                                                                                                                                                                                                                                          |

| LDAX             | B/D Reg. pair                                       | The contents of the designated register pair point to a memory<br>location. This instruction copies the contents of that memory<br>location into the accumulator. The contents of either the<br>register pair or the memory location are not altered.<br>Example: LDAX B                                 |

| Load reg         | ister pair immediate                    | The instruction loads 16-bit data in the register pair designated in the operand.                                                                                                                                                                                          |

|------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LXI              | Reg. pair, 16-bit data                  | Example: LXI H, 2034H or LXI H, XYZ                                                                                                                                                                                                                                        |

| Load H a<br>LHLD | nd L registers direct<br>16-bit address | The instruction copies the contents of the memory location<br>pointed out by the 16-bit address into register L and copies<br>the contents of the next memory location into register H. The<br>contents of source memory locations are not altered.<br>Example: LHLD 2040H |

| Store accu        | imulator direct                       |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STA               | 16-bit address                        | The contents of the accumulator are copied into the memory<br>location specified by the operand. This is a 3-byte instruction,<br>the second byte specifies the low-order address and the third<br>byte specifies the high-order address.<br>Example: STA 4350H                                                                                                                                                                              |

| Store accu        | mulator indirect                      |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| STAX              | Reg. pair                             | The contents of the accumulator are copied into the memory<br>location specified by the contents of the operand (register<br>pair). The contents of the accumulator are not altered.<br>Example: STAX B                                                                                                                                                                                                                                      |

| Store H ar        | nd L registers direct                 |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SHLD              | 16-bit address                        | The contents of register L are stored into the memory location<br>specified by the 16-bit address in the operand and the contents<br>of H register are stored into the next memory location by<br>incrementing the operand. The contents of registers HL are<br>not altered. This is a 3-byte instruction, the second byte<br>specifies the low-order address and the third byte specifies the<br>high-order address.<br>Example: SHLD 2470H |

| Exchange<br>XCHG  | H and L with D and E none             | The contents of register H are exchanged with the contents of register D, and the contents of register L are exchanged with the contents of register E.<br>Example: XCHG                                                                                                                                                                                                                                                                     |

|                   |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Copy H an<br>SPHL | nd L registers to the stack p<br>none | The instruction loads the contents of the H and L registers into<br>the stack pointer register, the contents of the H register<br>provide the high-order address and the contents of the L<br>register provide the low-order address. The contents of the H<br>and L registers are not altered.<br>Example: SPHL                                                                                                                             |

| Exchange<br>XTHL  | H and L with top of stack none        | The contents of the L register are exchanged with the stack location pointed out by the contents of the stack pointer                                                                                                                                                                                                                                                                                                                        |

| Push regis  | ter pair onto stack        |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PUSH        | Reg. pair                  | The contents of the register pair designated in the operand are<br>copied onto the stack in the following sequence. The stack<br>pointer register is decremented and the contents of the high-<br>order register (B, D, H, A) are copied into that location. The<br>stack pointer register is decremented again and the contents of<br>the low-order register (C, E, L, flags) are copied to that<br>location.<br>Example: PUSH B or PUSH A |

| Pop off sta | ack to register pair       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| POP         | Reg. pair                  | The contents of the memory location pointed out by the stack<br>pointer register are copied to the low-order register (C, E, L,<br>status flags) of the operand. The stack pointer is incremented<br>by 1 and the contents of that memory location are copied to<br>the high-order register (B, D, H, A) of the operand. The stack<br>pointer register is again incremented by 1.<br>Example: POP H or POP A                                |

| Output dat  | ta from accumulator to a p | ort with 8-bit address                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OUT         | 8-bit port address         | The contents of the accumulator are copied into the I/O port specified by the operand.<br>Example: OUT F8H                                                                                                                                                                                                                                                                                                                                  |

| Input data  | to accumulator from a por  | rt with 8-bit address                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IN          | 8-bit port address         | The contents of the input port designated in the operand are<br>read and loaded into the accumulator.<br>Example: IN 8CH                                                                                                                                                                                                                                                                                                                    |

|             |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **ARITHMETIC INSTRUCTIONS**

| Opcode           | Operand                             | Description                                                                                                                                                                                                                                                                                                                                                               |

|------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add regis<br>ADD | ter or memory to accumula<br>R<br>M | The contents of the operand (register or memory) are<br>added to the contents of the accumulator and the result is<br>stored in the accumulator. If the operand is a memory<br>location, its location is specified by the contents of the HL<br>registers. All flags are modified to reflect the result of the<br>addition.<br>Example: ADD B or ADD M                    |

| Add regis        | ter to accumulator with ca          | rry                                                                                                                                                                                                                                                                                                                                                                       |

| ADC              | R<br>M                              | The contents of the operand (register or memory) and<br>the Carry flag are added to the contents of the accumulator<br>and the result is stored in the accumulator. If the operand is a<br>memory location, its location is specified by the contents of<br>the HL registers. All flags are modified to reflect the result of<br>the addition.<br>Example: ADC B or ADC M |

| Add imm          | ediate to accumulator               |                                                                                                                                                                                                                                                                                                                                                                           |

| ADI              | 8-bit data                          | The 8-bit data (operand) is added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition. Example: ADI 45H                                                                                                                                                                          |

| Add imm          | ediate to accumulator with          | carry                                                                                                                                                                                                                                                                                                                                                                     |

| ACI              | 8-bit data                          | The 8-bit data (operand) and the Carry flag are added to the contents of the accumulator and the result is stored in the accumulator. All flags are modified to reflect the result of the addition.<br>Example: ACI 45H                                                                                                                                                   |

| Add regis        | ter pair to H and L register        | rs                                                                                                                                                                                                                                                                                                                                                                        |

| DAD              | Reg. pair                           | The 16-bit contents of the specified register pair are added to<br>the contents of the HL register and the sum is stored in the<br>HL register. The contents of the source register pair are not<br>altered. If the result is larger than 16 bits, the CY flag is set.<br>No other flags are affected.<br>Example: DAD H                                                  |

| Subtract r<br>SUB | register or memory from ac<br>R<br>M  | The contents of the operand (register or memory ) are<br>subtracted from the contents of the accumulator, and the result<br>is stored in the accumulator. If the operand is a memory<br>location, its location is specified by the contents of the HL<br>registers. All flags are modified to reflect the result of the<br>subtraction.<br>Example: SUB B or SUB M                                 |

|-------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subtract s<br>SBB | source and borrow from ac<br>R<br>M   | cumulator<br>The contents of the operand (register or memory ) and<br>the Borrow flag are subtracted from the contents of the<br>accumulator and the result is placed in the accumulator. If<br>the operand is a memory location, its location is specified by<br>the contents of the HL registers. All flags are modified to<br>reflect the result of the subtraction.<br>Example: SBB B or SBB M |

| Subtract i<br>SUI | mmediate from accumulat<br>8-bit data | or<br>The 8-bit data (operand) is subtracted from the contents of the<br>accumulator and the result is stored in the accumulator. All<br>flags are modified to reflect the result of the subtraction.<br>Example: SUI 45H                                                                                                                                                                          |

| Subtract :        | mmediate from accumulate              | on with homeow                                                                                                                                                                                                                                                                                                                                                                                     |

| SBI               | 8-bit data                            | The 8-bit data (operand) and the Borrow flag are subtracted<br>from the contents of the accumulator and the result is stored<br>in the accumulator. All flags are modified to reflect the result<br>of the subtracion.<br>Example: SBI 45H                                                                                                                                                         |

| Incremen<br>INR   | t register or memory by 1<br>R<br>M   | The contents of the designated register or memory) are<br>incremented by 1 and the result is stored in the same place. If<br>the operand is a memory location, its location is specified by<br>the contents of the HL registers.<br>Example: INR B or INR M                                                                                                                                        |

| Increment<br>INX  | t register pair by 1<br>R             | The contents of the designated register pair are incremented<br>by 1 and the result is stored in the same place.<br>Example: INX H                                                                                                                                                                                                                                                                 |

| Decremen<br>DCR | nt register or memory by 1<br>R<br>M | The contents of the designated register or memory are<br>decremented by 1 and the result is stored in the same place. If<br>the operand is a memory location, its location is specified by<br>the contents of the HL registers.<br>Example: DCR B or DCR M                                                                                                    |

|-----------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Decremen        | nt register pair by 1                |                                                                                                                                                                                                                                                                                                                                                               |

| DCX             | R                                    | The contents of the designated register pair are decremented<br>by 1 and the result is stored in the same place.<br>Example: DCX H                                                                                                                                                                                                                            |

| Decimal a       | adjust accumulator                   |                                                                                                                                                                                                                                                                                                                                                               |

| DAA             | none                                 | The contents of the accumulator are changed from a binary<br>value to two 4-bit binary coded decimal (BCD) digits. This is<br>the only instruction that uses the auxiliary flag to perform the<br>binary to BCD conversion, and the conversion procedure is<br>described below. S, Z, AC, P, CY flags are altered to reflect<br>the results of the operation. |

|                 |                                      | If the value of the low-order 4-bits in the accumulator is greater than 9 or if AC flag is set, the instruction adds 6 to the low-order four bits.                                                                                                                                                                                                            |

|                 |                                      | If the value of the high-order 4-bits in the accumulator is greater than 9 or if the Carry flag is set, the instruction adds 6 to the high-order four bits.                                                                                                                                                                                                   |

|                 |                                      | Example: DAA                                                                                                                                                                                                                                                                                                                                                  |

# **BRANCHING INSTRUCTIONS**

| Opcode          | Operand                        | Description                                                                                                                                    |

|-----------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Jump unc<br>JMP | onditionally<br>16-bit address | The program sequence is transferred to the memory location specified by the 16-bit address given in the operand. Example: JMP 2034H or JMP XYZ |

|                 |                                |                                                                                                                                                |

Jump conditionally

Operand: 16-bit address

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Example: JZ 2034H or JZ XYZ

| Opcode | Description         | Flag Status      |

|--------|---------------------|------------------|

| JC     | Jump on Carry       | CY = 1           |

| JNC    | Jump on no Carry    | CY = 0           |

| JP     | Jump on positive    | $\mathbf{S} = 0$ |

| JM     | Jump on minus       | S = 1            |

| JZ     | Jump on zero        | $\mathbf{Z} = 1$ |

| JNZ    | Jump on no zero     | $\mathbf{Z} = 0$ |

| JPE    | Jump on parity even | P = 1            |

| JPO    | Jump on parity odd  | $\mathbf{P} = 0$ |

| Unconditional subroutine call                                                                                                                                                                                                           |                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| CALL 16-bit address The program sequence is transferred to the specified by the 16-bit address given in the transfer, the address of the next instruction (the contents of the program counter) is puse Example: CALL 2034H or CALL XYZ | he operand. Before<br>uction after CALL |

## Call conditionally

# Operand: 16-bit address

The program sequence is transferred to the memory location specified by the 16-bit address given in the operand based on the specified flag of the PSW as described below. Before the transfer, the address of the next instruction after the call (the contents of the program counter) is pushed onto the stack. Example: CZ 2034H or CZ XYZ

| Description         | Flag Status                                                                                                                      |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Call on Carry       | $\mathbf{C}\mathbf{Y} = 1$                                                                                                       |

| Call on no Carry    | $\mathbf{C}\mathbf{Y}=0$                                                                                                         |

| Call on positive    | $\mathbf{S} = 0$                                                                                                                 |

| Call on minus       | S = 1                                                                                                                            |

| Call on zero        | $\mathbf{Z} = 1$                                                                                                                 |

| Call on no zero     | $\mathbf{Z} = 0$                                                                                                                 |

| Call on parity even | $\mathbf{P} = 1$                                                                                                                 |

| Call on parity odd  | $\mathbf{P} = 0$                                                                                                                 |

|                     | Call on Carry<br>Call on no Carry<br>Call on positive<br>Call on minus<br>Call on zero<br>Call on no zero<br>Call on parity even |

Return from subroutine unconditionally

RET none

The program sequence is transferred from the subroutine to the calling program. The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address.

Example: RET

Return from subroutine conditionally

Operand: none

The program sequence is transferred from the subroutine to the calling program based on the specified flag of the PSW as described below. The two bytes from the top of the stack are copied into the program counter, and program execution begins at the new address. Example: RZ

| Opcode<br>RC<br>RNC<br>RP | Description<br>Return on Carry<br>Return on no Carry<br>Return on positive | Flag Status<br>CY = 1<br>CY = 0<br>S = 0 |

|---------------------------|----------------------------------------------------------------------------|------------------------------------------|

| RP<br>RM                  | Return on positive<br>Return on minus                                      | S = 0 $S = 1$                            |

| RZ<br>RNZ                 | Return on zero                                                             | Z = 1                                    |

| RPE<br>RPO                | Return on no zero<br>Return on parity even<br>Return on parity odd         | Z = 0 $P = 1$ $P = 0$                    |

| 14.0                      | Return on purity oud                                                       | $\mathbf{I} = 0$                         |

#### Load program counter with HL contents

none

The contents of registers H and L are copied into the program counter. The contents of H are placed as the high-order byte and the contents of L as the low-order byte. Example: PCHL

Restart RST 0-7

The RST instruction is equivalent to a 1-byte call instruction to one of eight memory locations depending upon the number. The instructions are generally used in conjunction with interrupts and inserted using external hardware. However these can be used as software instructions in a program to transfer program execution to one of the eight locations. The addresses are:

| Instruction | Restart Address |

|-------------|-----------------|

| RST 0       | 0000H           |

| RST 1       | 0008H           |

| RST 2       | 0010H           |

| RST 3       | 0018H           |

| RST 4       | 0020H           |

| RST 5       | 0028H           |

| RST 6       | 0030H           |

| RST 7       | 0038H           |

The 8085 has four additional interrupts and these interrupts generate RST instructions internally and thus do not require any external hardware. These instructions and their Restart addresses are:

| Restart Address |

|-----------------|

| 0024H           |

| 002CH           |

| 0034H           |

| 003CH           |

|                 |

# LOGICAL INSTRUCTIONS

| Opcode           | Operand                                | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compare<br>CMP   | register or memory with a<br>R<br>M    | ccumulator<br>The contents of the operand (register or memory) are<br>compared with the contents of the accumulator. Both<br>contents are preserved . The result of the comparison is<br>shown by setting the flags of the PSW as follows:<br>if (A) < (reg/mem): carry flag is set<br>if (A) = (reg/mem): zero flag is set<br>if (A) > (reg/mem): carry and zero flags are reset<br>Example: CMP B or CMP M |

| Compare          | immediate with accumula                | tor                                                                                                                                                                                                                                                                                                                                                                                                          |

| CPI              | 8-bit data                             | The second byte (8-bit data) is compared with the contents of<br>the accumulator. The values being compared remain<br>unchanged. The result of the comparison is shown by setting<br>the flags of the PSW as follows:<br>if (A) < data: carry flag is set<br>if (A) = data: zero flag is set<br>if (A) > data: carry and zero flags are reset<br>Example: CPI 89H                                            |

| Logical A        | ND register or memory w                | rith accumulator                                                                                                                                                                                                                                                                                                                                                                                             |

| ANA              | R<br>M                                 | The contents of the accumulator are logically ANDed with<br>the contents of the operand (register or memory), and the<br>result is placed in the accumulator. If the operand is a<br>memory location, its address is specified by the contents of<br>HL registers. S, Z, P are modified to reflect the result of the<br>operation. CY is reset. AC is set.<br>Example: ANA B or ANA M                        |

| Logical A<br>ANI | AND immediate with accur<br>8-bit data | mulator<br>The contents of the accumulator are logically ANDed with the<br>8-bit data (operand) and the result is placed in the<br>accumulator. S, Z, P are modified to reflect the result of the<br>operation. CY is reset. AC is set.<br>Example: ANI 86H                                                                                                                                                  |

| Exclusive<br>XRA  | OR register or memory w<br>R<br>M     | ith accumulator<br>The contents of the accumulator are Exclusive ORed with<br>the contents of the operand (register or memory), and the<br>result is placed in the accumulator. If the operand is a<br>memory location, its address is specified by the contents of<br>HL registers. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: XRA B or XRA M |

|-------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Exclusive         | OR immediate with accur               | nulator                                                                                                                                                                                                                                                                                                                                                                                              |

| XRI               | 8-bit data                            | The contents of the accumulator are Exclusive ORed with the<br>8-bit data (operand) and the result is placed in the<br>accumulator. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: XRI 86H                                                                                                                                                         |

| Logical O<br>ORA  | R register or memory with<br>R<br>M   | n accumulaotr<br>The contents of the accumulator are logically ORed with<br>the contents of the operand (register or memory), and the<br>result is placed in the accumulator. If the operand is a<br>memory location, its address is specified by the contents of<br>HL registers. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: ORA B or ORA M   |

| Logical O<br>ORI  | R immediate with accumu<br>8-bit data | lator<br>The contents of the accumulator are logically ORed with the<br>8-bit data (operand) and the result is placed in the<br>accumulator. S, Z, P are modified to reflect the result of the<br>operation. CY and AC are reset.<br>Example: ORI 86H                                                                                                                                                |

| Rotate acc        | cumulator left                        |                                                                                                                                                                                                                                                                                                                                                                                                      |

| RLC               | none                                  | Each binary bit of the accumulator is rotated left by one<br>position. Bit D7 is placed in the position of D0 as well as in<br>the Carry flag. CY is modified according to bit D7. S, Z, P,<br>AC are not affected.<br>Example: RLC                                                                                                                                                                  |

| Rotate acc<br>RRC | cumulator right<br>none               | Each binary bit of the accumulator is rotated right by one<br>position. Bit D <sub>0</sub> is placed in the position of D <sub>7</sub> as well as in<br>the Carry flag. CY is modified according to bit D <sub>0</sub> . S, Z, P,<br>AC are not affected.<br>Example: RRC                                                                                                                            |

| Rotate acc       | cumulator left through car | 'Y                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAL              | none                       | Each binary bit of the accumulator is rotated left by one position through the Carry flag. Bit D7 is placed in the Carry                                                                                                                                                                        |

|                  |                            | flag, and the Carry flag is placed in the least significant<br>position D <sub>0</sub> . CY is modified according to bit D <sub>7</sub> . S, Z, P, AC                                                                                                                                           |

|                  |                            | are not affected.<br>Example: RAL                                                                                                                                                                                                                                                               |

| Rotate acc       | cumulator right through ca | rry                                                                                                                                                                                                                                                                                             |

| RAR              | none                       | Each binary bit of the accumulator is rotated right by one<br>position through the Carry flag. Bit D0 is placed in the Carry<br>flag, and the Carry flag is placed in the most significant<br>position D7. CY is modified according to bit D0. S, Z, P, AC<br>are not affected.<br>Example: RAR |

| Complem          | ent accumulator            |                                                                                                                                                                                                                                                                                                 |

| CMA              | none                       | The contents of the accumulator are complemented. No flags<br>are affected.<br>Example: CMA                                                                                                                                                                                                     |

| Complem          | ent carry                  |                                                                                                                                                                                                                                                                                                 |

| CMC              | none                       | The Carry flag is complemented. No other flags are affected.<br>Example: CMC                                                                                                                                                                                                                    |

| Set Carry<br>STC | none                       | The Carry flag is set to 1. No other flags are affected.<br>Example: STC                                                                                                                                                                                                                        |

# **CONTROL INSTRUCTIONS**

| Opcode           | Operand          | Description                                                                                                                                                                                                                                                                                                                           |

|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No operat<br>NOP | tion<br>none     | No operation is performed. The instruction is fetched and decoded. However no operation is executed. Example: NOP                                                                                                                                                                                                                     |

| Halt and e       | enter wait state |                                                                                                                                                                                                                                                                                                                                       |

| HLT              | none             | The CPU finishes executing the current instruction and halts<br>any further execution. An interrupt or reset is necessary to<br>exit from the halt state.<br>Example: HLT                                                                                                                                                             |

| Disable ir       | nterrupts        |                                                                                                                                                                                                                                                                                                                                       |

| DI               | none             | The interrupt enable flip-flop is reset and all the interrupts except the TRAP are disabled. No flags are affected. Example: DI                                                                                                                                                                                                       |

| Enable in        | terrupts         |                                                                                                                                                                                                                                                                                                                                       |

| EI               | none             | The interrupt enable flip-flop is set and all interrupts are<br>enabled. No flags are affected. After a system reset or the<br>acknowledgement of an interrupt, the interrupt enable flip-<br>flop is reset, thus disabling the interrupts. This instruction is<br>necessary to reenable the interrupts (except TRAP).<br>Example: EI |

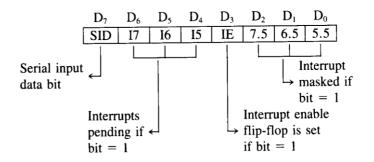

Read interrupt mask RIM none

This is a multipurpose instruction used to read the status of interrupts 7.5, 6.5, 5.5 and read serial data input bit. The instruction loads eight bits in the accumulator with the following interpretations.

Example: RIM

Set interrupt mask

SIM none This is a multipurpose instruction and used to implement the 8085 interrupts 7.5, 6.5, 5.5, and serial data output.

# **Instruction word size**

The 8085 instruction set is classified into the following three groups according to word size:

- **1.** One-word or 1-byte instructions

- **2.** Two-word or 2-byte instructions

- **3.** Three-word or 3-byte instructions

In the 8085, "byte" and "word" are synonymous because it is an 8-bit microprocessor. However, instructions are commonly referred to in terms of bytes rather than words.

# **One-Byte Instructions**

A 1-byte instruction includes the opcode and operand in the same byte. Operand(s) are internal register and are coded into the instruction. For example:

| Task                                                               | Op<br>code | Operand | Binary<br>Code | Hex<br>Code |

|--------------------------------------------------------------------|------------|---------|----------------|-------------|

| Copy the contents of the accumulator in the register C.            | MOV        | C,A     | 0100 1111      | 4FH         |

| Add the contents of register B to the contents of the accumulator. | ADD        | В       | 1000 0000      | 80H         |

| Invert (compliment) each bit in the accumulator.                   | СМА        |         | 0010 1111      | 2FH         |

These instructions are 1-byte instructions performing three different tasks. In the first instruction, both operand registers are specified. In the second instruction, the operand B is specified and the accumulator is assumed. Similarly, in the third instruction, the accumulator is assumed to be the implicit operand. These instructions are stored in 8-

bit binary format in memory; each requires one memory location.

MOV rd, rs rd < rs copies contents of source register (rs) into destination register (rd). Coded as 01 ddd sss where ddd is a code for one of the 7 general registers which is the destination of the data, sss is the code of the source register.

Example: MOV A,B Coded as 01111000 = 78H = 170 octal (octal was used extensively in instruction design of such processors).

# $\begin{array}{l} ADD \ r \\ A < A + r \end{array}$

# Two-Byte Instructions

In a two-byte instruction, the first byte specifies the operation code and the second byte specifies the operand. Source operand is a data byte immediately following the opcode. For example:

| Task                                              | Opcode | Operand | Binary<br>Code | Hex Code   |                           |

|---------------------------------------------------|--------|---------|----------------|------------|---------------------------|

| Load an 8-bit data<br>byte in the<br>accumulator. | MVI    | A, Data | 0011 1110      | 3E<br>Data | First Byte<br>Second Byte |

|                                                   |        |         | DATA           |            | -                         |

Assume that the data byte is 32H. The assembly language instruction is written as

| Mnemonics  | Hex code |

|------------|----------|

| MVI A, 32H | 3E 32H   |

The instruction would require two memory locations to store in memory.

# MVI r,data

r < data

Example: MVI A,30H coded as 3EH 30H as two contiguous bytes. This is an example of immediate addressing.

$\begin{array}{l} ADI \ data \\ A < \ A + \ data \end{array}$

OUT port

where port is an 8-bit device address. (Port) <-- A. Since the byte is not the data but points directly to where it is located this is called direct addressing.

# **Three-Byte Instructions**

In a three-byte instruction, the first byte specifies the opcode, and the following two bytes specify the 16-bit address. Note that the second byte is the low-order address and the third byte is the high-order address. opcode + data byte + data byte

For example:

| Task         | Opcode | Operand | Binary code | Hex Code |             |

|--------------|--------|---------|-------------|----------|-------------|

| Transfer the | JMP    | 2085H   |             | C3       | First byte  |

| program      |        |         | 1100 0011   |          |             |

| sequence to  |        |         | 1000 0101   | 85       | Second Byte |

| the memory   |        |         | 1000 0101   |          |             |

| location     |        |         | 0010 0000   | 20       | Third Byte  |

| 2085H.       |        |         |             |          |             |

This instruction would require three memory locations to store in memory.

Three byte instructions - opcode + data byte + data byte

LXI rp, data16

rp is one of the pairs of registers BC, DE, HL used as 16-bit registers. The two data bytes are 16-bit data in L H order of significance.

rp <-- data16

Example:

LXI H,0520H coded as 21H 20H 50H in three bytes. This is also immediate addressing.

LDA addr

A <-- (addr) Addr is a 16-bit address in L H order. Example: LDA 2134H coded as 3AH 34H 21H. This is also an example of direct addressing.